STM32 F4VE: diferenças entre revisões

Sem resumo de edição |

Sem resumo de edição |

||

| Linha 3: | Linha 3: | ||

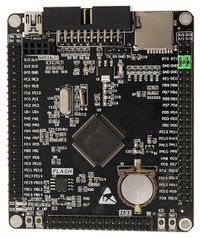

[[File:STM32F407VET6 Legend.jpg|200px|thumb|Features]] | [[File:STM32F407VET6 Legend.jpg|200px|thumb|Features]] | ||

== | == Overview == | ||

The STM32 F4VE is a small development board based on the STM32F407VET6 microcontroller. | |||

It breaks out all CPU pins via two 2×24 pin headers and supports expansion through | |||

multiple peripheral connectors. | |||

Board marked "STM32F4XX STM32_F4VE V2.0 1509" on the back. | Board marked "STM32F4XX STM32_F4VE V2.0 1509" on the back. | ||

{| class="wikitable" | {| class="wikitable" | ||

! colspan="2" | Board | ! colspan="2" | Board | ||

| Linha 62: | Linha 26: | ||

|} | |} | ||

== | === Warnings === | ||

* | * '''Warning:''' The +5V pins are directly connected to the USB +5V pin with no protection. Do not power the board through USB and an external power supply at the same time. | ||

* '''Warning:''' The board has an extra pull-up resistor on D+ (R21, 1.5kΩ) that violates the USB specification when the MCU's internal pull-ups are also active. This may cause USB errors. USB data lines also have 22Ω series resistors (R18, R19) for protection. | |||

* | |||

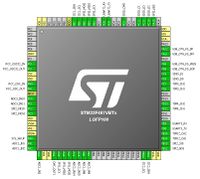

=== | == Microcontroller == | ||

{| class="wikitable" | {| class="wikitable" | ||

! colspan="2" | ! colspan="2" | STM32F407VET6 | ||

|- | |- | ||

| Manufacturer || ST Microelectronics | | Manufacturer || ST Microelectronics | ||

|- | |- | ||

| Core || ARM Cortex-M4 32-bit | | Core || ARM Cortex-M4 32-bit + FPU | ||

|- | |- | ||

| Max. Clock || 168 MHz | | Max. Clock || 168 MHz | ||

|- | |- | ||

| Operating Voltage || 1.8V – 3.6V | | Operating Voltage || 1.8V – 3.6V | ||

| Linha 99: | Linha 47: | ||

{| class="wikitable" | {| class="wikitable" | ||

! colspan="2" | | ! colspan="2" | Memory | ||

|- | |- | ||

| Flash || 512 KiB | | Flash || 512 KiB | ||

| Linha 109: | Linha 57: | ||

{| class="wikitable" | {| class="wikitable" | ||

! colspan="2" | | ! colspan="2" | Oscillators | ||

|- | |- | ||

| HSI || 16 MHz | | HSI || 16 MHz | ||

| Linha 115: | Linha 63: | ||

| LSI || 32 kHz | | LSI || 32 kHz | ||

|- | |- | ||

| HSE || 8 MHz | | HSE || 8 MHz (Y2) | ||

|- | |- | ||

| LSE || 32.768 kHz | | LSE || 32.768 kHz (Y1) | ||

|} | |} | ||

=== | === Peripherals === | ||

* 3× SPI | * 3× SPI | ||

* 3× USART + 2× UART | * 3× USART + 2× UART | ||

| Linha 128: | Linha 76: | ||

* 1× SDIO | * 1× SDIO | ||

* 2× CAN | * 2× CAN | ||

* 1× USB 2.0 FS/HS ( | * 1× USB 2.0 FS/HS (with DMA) | ||

* 1× USB HS ULPI ( | * 1× USB HS ULPI (for external PHY) | ||

* 1× | * 1× 10/100 Ethernet MAC | ||

* 1× | * 1× 8–12-bit parallel camera interface | ||

* 3× ADC 12-bit (1 µs) | * 3× ADC 12-bit (1 µs) | ||

* 2× DAC 12-bit | * 2× DAC 12-bit | ||

* | * Single-cycle DSP instructions | ||

== Board Hardware == | |||

== | === Power === | ||

{| class="wikitable" | {| class="wikitable" | ||

! colspan="2" | Regulator | ! colspan="2" | Voltage Regulator — AMS1117-3.3V (U1) | ||

|- | |- | ||

| | | Input || +4.6V to +15V | ||

|- | |||

| Output || +3.3V @ 1A | |||

|- | |- | ||

| Package || SOT223 | | Package || SOT223 | ||

|- | |- | ||

| | | Power Sources || +5V pin, +3.3V pin, USB | ||

|} | |||

=== LEDs === | |||

{| class="wikitable" | |||

! Ref !! GPIO !! Resistor !! Mode | |||

|- | |- | ||

| | | D1 (Power) || +3.3V rail || R5 (510Ω) || Always on | ||

|- | |||

| D2 (User) || PA6 || R13 (510Ω) || Sink (active low) | |||

|- | |||

| D3 (User) || PA7 || R14 (510Ω) || Sink (active low) | |||

|} | |} | ||

== | === Buttons === | ||

{| class="wikitable" | {| class="wikitable" | ||

! | ! Label !! GPIO !! Mode | ||

|- | |- | ||

| | | RST || NRST || Active low | ||

|- | |- | ||

| | | K_UP || PA0 || Active high | ||

|- | |- | ||

| | | K0 || PE4 || Active low | ||

|- | |- | ||

| | | K1 || PE3 || Active low | ||

|} | |||

=== Boot Mode Jumpers === | |||

{| class="wikitable" | |||

! Label !! Connected to !! Notes | |||

|- | |- | ||

| | | BT0 || BOOT0 || Part of Header 2 (J3, pin 5). GND via R7 by default. | ||

|- | |- | ||

| | | BT1 || PB2 (BOOT1) || Part of Header 2 (J3, pin 6). GND via R8 by default. | ||

|} | |||

''Note: Both BOOT pins are pulled to GND by default (R7, R8 = 10kΩ), booting from flash. Jumper caps are pre-installed for convenience.'' | |||

=== On-board Devices === | |||

{| class="wikitable" | |||

! colspan="2" | SPI Flash — W25Q16 (U3) | |||

|- | |- | ||

| | | Capacity || 2 MiB (16 Mbit) | ||

|- | |- | ||

| | | Interface || SPI1 | ||

|- | |- | ||

| | | Package || SOP-8 | ||

|- | |- | ||

| | | /CS (F_CS) || PB0 (10kΩ pull-up via R20) | ||

|- | |- | ||

| | | DO (MISO) || PB4 / SPI1_MISO | ||

|- | |- | ||

| | | DI (MOSI) || PB5 / SPI1_MOSI | ||

|- | |- | ||

| | | CLK || PB3 / SPI1_SCK | ||

|- | |- | ||

| | | /WP || +3.3V (always writable) | ||

|- | |- | ||

| | | /HOLD || +3.3V | ||

|} | |||

{| class="wikitable" | |||

! colspan="2" | RTC Backup Battery | |||

|- | |- | ||

| | | Type || CR1220 | ||

|- | |- | ||

| | | Protection || BAT54C dual Schottky diode (Q1) | ||

|} | |||

== Connectors & Pinouts == | |||

=== GPIO Headers === | |||

Two 2×24 pin headers (2.54mm, male) break out all GPIO. | |||

'''Note:''' PB3, PB5, PB6, PB7 are shared with the nRF24L01 header (SPI1). PB3/PB4 are also used for JTAG (TDO/TRST). PA13/PA14 are JTAG only and do not appear on the GPIO headers. | |||

<div style="display:flex; gap:2em; flex-wrap:wrap;"> | |||

{| class="wikitable" | |||

|+ Header 1 — J2 | |||

! Pin !! GPIO !! !! GPIO !! Pin | |||

|- | |- | ||

| | | 1 || 5V || || 5V || 2 | ||

|- | |- | ||

| | | 3 || 5V || || 5V || 4 | ||

|- | |- | ||

| | | 5 || 3V3 || || 3V3 || 6 | ||

|- | |- | ||

| | | 7 || 3V3 || || 3V3 || 8 | ||

|- | |- | ||

| | | 9 || GND || || GND || 10 | ||

|- | |- | ||

| | | 11 || PE2 || || PE3 || 12 | ||

|- | |- | ||

| | | 13 || PE4 || || PE5 || 14 | ||

|- | |- | ||

| | | 15 || PE6 || || PC13 || 16 | ||

|- | |- | ||

| | | 17 || PC0 || || PC1 || 18 | ||

|- | |- | ||

| | | 19 || PC2 || || PC3 || 20 | ||

|- | |- | ||

| | | 21 || VREF- || || VREF+ || 22 | ||

|- | |- | ||

| | | 23 || PA0 || || PA1 || 24 | ||

|- | |- | ||

| | | 25 || PA2 || || PA3 || 26 | ||

|- | |- | ||

| | | 27 || PA4 || || PA5 || 28 | ||

|- | |- | ||

| | | 29 || PA6 || || PA7 || 30 | ||

|- | |- | ||

| | | 31 || PC4 || || PC5 || 32 | ||

|- | |- | ||

| | | 33 || PB0 || || PB1 || 34 | ||

|- | |- | ||

| | | 35 || PE7 || || PE8 || 36 | ||

|- | |- | ||

| | | 37 || PE9 || || PE10 || 38 | ||

|- | |- | ||

| | | 39 || PE11 || || PE12 || 40 | ||

|- | |- | ||

| | | 41 || PE13 || || PE14 || 42 | ||

|- | |- | ||

| | | 43 || PE15 || || PB10 || 44 | ||

|- | |- | ||

| | | 45 || PB11 || || PB12 || 46 | ||

|- | |- | ||

| | | 47 || PB13 || || PB14 || 48 | ||

|} | |} | ||

{| class="wikitable" | {| class="wikitable" | ||

! | |+ Header 2 — J3 | ||

! Pin !! GPIO !! !! GPIO !! Pin | |||

|- | |- | ||

| | | 1 || 3V3 || || 3V3 || 2 | ||

|- | |- | ||

| | | 3 || 3V3 || || 3V3 || 4 | ||

|- | |- | ||

| | | 5 || BT0 (BOOT0) || || BT1 (PB2) || 6 | ||

|- | |- | ||

| | | 7 || GND || || GND || 8 | ||

|- | |- | ||

| | | 9 || GND || || GND || 10 | ||

|- | |- | ||

| | | 11 || PE1 || || PE0 || 12 | ||

|- | |- | ||

| 13 || PB9 || | | 13 || PB9 || || PB8 || 14 | ||

|- | |- | ||

| | | 15 || PB7 ¹ || || PB6 ¹ || 16 | ||

|- | |- | ||

| | | 17 || PB5 ¹ || || PB3 ¹ || 18 | ||

|- | |- | ||

| | | 19 || PD7 || || PD6 || 20 | ||

|- | |- | ||

| | | 21 || PD5 || || PD4 || 22 | ||

|- | |- | ||

| | | 23 || PD3 || || PD2 || 24 | ||

|- | |- | ||

| | | 25 || PD1 || || PD0 || 26 | ||

|- | |- | ||

| | | 27 || PC12 || || PC11 || 28 | ||

|- | |- | ||

| | | 29 || PC10 || || PA15 || 30 | ||

|- | |- | ||

| | | 31 || PA12 || || PA11 || 32 | ||

|- | |- | ||

| | | 33 || PA10 || || PA9 || 34 | ||

|- | |- | ||

| | | 35 || PA8 || || PC9 || 36 | ||

|- | |- | ||

| | | 37 || PC8 || || PC7 || 38 | ||

|- | |- | ||

| | | 39 || PC6 || || PD15 || 40 | ||

|- | |- | ||

| | | 41 || PD14 || || PD13 || 42 | ||

|- | |- | ||

| | | 43 || PD12 || || PD11 || 44 | ||

|- | |- | ||

| | | 45 || PD10 || || PD9 || 46 | ||

|- | |- | ||

| 47 || PD8 || || PB15 || 48 | |||

| 47 || PD8 || | |||

|} | |} | ||

</div> | |||

=== JTAG Header (P1) — 2×10 === | ¹ Shared with nRF24L01 header (SPI1): PB3=SCK, PB5=MOSI, PB6=CE, PB7=CS. | ||

=== JTAG / SWD Header (P1) — 2×10 === | |||

{| class="wikitable" | {| class="wikitable" | ||

! | ! Pin !! Function !! !! Function !! Pin | ||

|- | |||

| 1 || +3.3V || || +3.3V || 2 | |||

|- | |||

| 3 || TRST (PB4) || || GND || 4 | |||

|- | |- | ||

| | | 5 || TDI (PA15) || || GND || 6 | ||

|- | |- | ||

| | | 7 || TMS/SWDIO (PA13) || || GND || 8 | ||

|- | |- | ||

| | | 9 || TCLK/SWCLK (PA14) || || GND || 10 | ||

|- | |- | ||

| | | 11 || RTCK (N.C.) || || GND || 12 | ||

|- | |- | ||

| | | 13 || TDO/SWO (PB3) || || GND || 14 | ||

|- | |- | ||

| | | 15 || RESET (NRST) || || GND || 16 | ||

|- | |- | ||

| | | 17 || N.C. || || GND || 18 | ||

|- | |- | ||

| | | 19 || N.C. || || GND || 20 | ||

|} | |} | ||

=== TFT LCD Header (J1) — 2×16 === | === TFT LCD Header (J1) — 2×16 === | ||

{| class="wikitable" | {| class="wikitable" | ||

! | ! Pin !! Function !! !! Function !! Pin | ||

|- | |- | ||

| 1 || GND || | | 1 || GND || || RST || 2 | ||

|- | |- | ||

| | | 3 || FSMC_D15 (PD10) || || FSMC_D14 (PD9) || 4 | ||

|- | |- | ||

| | | 5 || FSMC_D13 (PD8) || || FSMC_D12 (PE15) || 6 | ||

|- | |- | ||

| | | 7 || FSMC_D11 (PE14) || || FSMC_D10 (PE13) || 8 | ||

|- | |- | ||

| | | 9 || FSMC_D9 (PE12) || || FSMC_D8 (PE11) || 10 | ||

|- | |- | ||

| | | 11 || FSMC_D7 (PE10) || || FSMC_D6 (PE9) || 12 | ||

|- | |- | ||

| | | 13 || FSMC_D5 (PE8) || || FSMC_D4 (PE7) || 14 | ||

|- | |- | ||

| | | 15 || FSMC_D3 (PD1) || || FSMC_D2 (PD0) || 16 | ||

|- | |- | ||

| | | 17 || FSMC_D1 (PD15) || || FSMC_D0 (PD14) || 18 | ||

|- | |- | ||

| | | 19 || FSMC_NOE (PD4) || || FSMC_NWE (PD5) || 20 | ||

|- | |- | ||

| | | 21 || FSMC_A18 (PD13) || || FSMC_NE1 (PD7) || 22 | ||

|- | |- | ||

| | | 23 || Touch_CLK (PB13) || || Touch_CS (PB12) || 24 | ||

|- | |- | ||

| | | 25 || Touch_MOSI (PB15) || || Touch_MISO (PB14) || 26 | ||

|- | |- | ||

| | | 27 || Touch_PEN (PC5) || || LCD_BL (PB1) ² || 28 | ||

|- | |- | ||

| 30 | | 29 || VBAT (N.C.) || || GND || 30 | ||

|- | |||

| 31 || +3.3V || || GND || 32 | |||

|} | |} | ||

² LCD backlight (PB1) is driven via PNP transistor Q2, not directly. | |||

=== nRF24L01 Header (JP2) — 2×4 === | === nRF24L01 Header (JP2) — 2×4 === | ||

{| class="wikitable" | {| class="wikitable" | ||

! | ! Pin !! Function !! !! Function !! Pin | ||

|- | |- | ||

| | | 1 || GND || || VCC (+3.3V) || 2 | ||

|- | |- | ||

| | | 3 || CE (PB6) || || CSN (PB7) || 4 | ||

|- | |- | ||

| | | 5 || SCK (PB3) || || MOSI (PB5) || 6 | ||

|- | |- | ||

| | | 7 || MISO (PB4) || || IRQ (PB8) || 8 | ||

|} | |} | ||

=== Serial Header (J6) — 1×4 === | === Serial Header (J6) — 1×4 === | ||

{| class="wikitable" | {| class="wikitable" | ||

! | ! Pin !! Function !! GPIO | ||

|- | |- | ||

| 1 || VCC || +5V | | 1 || VCC || +5V | ||

| Linha 412: | Linha 366: | ||

| 2 || GND || Ground | | 2 || GND || Ground | ||

|- | |- | ||

| 3 || RX || PA10 | | 3 || RX || PA10 (USART1_RX) | ||

|- | |- | ||

| 4 || TX || PA9 | | 4 || TX || PA9 (USART1_TX) | ||

|} | |} | ||

=== | === MiniSD Connector (U5) === | ||

{| class="wikitable" | {| class="wikitable" | ||

! | ! Pin !! Function !! GPIO | ||

|- | |- | ||

| 1 || DAT2 || PC10 | | 1 || DAT2 || PC10 (SDIO_D2) | ||

|- | |- | ||

| 2 || CD/DAT3 || PC11 | | 2 || CD/DAT3 || PC11 (SDIO_D3) | ||

|- | |- | ||

| 3 || CMD || PD2 | | 3 || CMD || PD2 (SDIO_CMD) | ||

|- | |- | ||

| 4 || VDD || +3.3V | | 4 || VDD || +3.3V | ||

|- | |- | ||

| 5 || CLK || PC12 | | 5 || CLK || PC12 (SDIO_SCK) | ||

|- | |- | ||

| 6 || VSS || Ground | | 6 || VSS || Ground | ||

|- | |- | ||

| 7 || DAT0 || PC8 | | 7 || DAT0 || PC8 (SDIO_D0) | ||

|- | |- | ||

| 8 || DAT1 || PC9 | | 8 || DAT1 || PC9 (SDIO_D1) | ||

|- | |||

| 9 || CD || N.C. | |||

|} | |} | ||

''Note: SDIO data lines and CMD have 10kΩ pull-up resistors (R24, R26–R29).'' | |||

=== USB Mini (J4) === | === USB Mini Connector (J4) === | ||

{| class="wikitable" | {| class="wikitable" | ||

! | ! Pin !! Function !! GPIO | ||

|- | |- | ||

| 1 || VCC || +5V | | 1 || VCC || +5V | ||

|- | |- | ||

| 2 || D- || PA11 | | 2 || D- || PA11 (USB_DM), 22Ω series (R19) | ||

|- | |||

| 3 || D+ || PA12 (USB_DP), 22Ω series (R18), 1.5kΩ pull-up (R21) | |||

|- | |- | ||

| | | 4 || ID || N.C. | ||

|- | |- | ||

| 5 || GND || Ground | | 5 || GND || Ground | ||

|} | |} | ||

== | == Development == | ||

=== Toolchain === | |||

Generate the project with '''STM32CubeMX''' in '''Makefile''' format, then compile with the [https://developer.arm.com/open-source/gnu-toolchain/gnu-rm GNU ARM Embedded Toolchain]. | |||

=== Flashing === | |||

Use an '''ST-Link V2''' programmer and the [https://github.com/texane/stlink stlink] software: | |||

<syntaxhighlight lang="shell"> | |||

st-flash write build/blinky.bin 0x8000000 | |||

</syntaxhighlight> | |||

=== Debugging === | |||

Run '''st-util''' in a separate terminal, then launch GDB: | |||

<syntaxhighlight lang="shell"> | |||

arm-none-eabi-gdb --eval-command="tar extended-remote :4242" build/blinky.elf | |||

</syntaxhighlight> | |||

== Documentation == | |||

[[File:STM32F407VET6 Pinmap.jpg|200px|thumb|Pinmap]] | |||

* Board schematic (ZET6 variant — mostly applicable): [[Media:STM32F407ZET6_sch-1.pdf]] | |||

** Note: MCU pin numbers differ; I/O connectors have fewer pins; SDRAM not present on this board. | |||

* Alternative schematic with PCB layout and BOM: [[Media:STM32_F4VE_SCHEMATIC.PDF]] | |||

* Original schematic: [https://stm32-base.org/assets/pdf/boards/original-schematic-STM32F407VET6-STM32_F4VE_V2.0.pdf STM32_F4VE_V2.0 Schematic (stm32-base.org)] | |||

* Demo software translated manual: [[Media:STM32F407_example_manual.ja.en.pdf]] | |||

== External | == External Links == | ||

* [ | * [https://www.st.com/en/microcontrollers-microprocessors/stm32f407ve.html STM32F407VE Product Page — ST] | ||

* [ | * [https://www.st.com/resource/en/reference_manual/dm00031020.pdf STM32F4 Reference Manual] | ||

* [ | * [https://www.st.com/en/development-tools/stm32cubemx.html STM32CubeMX] | ||

* [https://stm32-base.org/boards/STM32F407VET6-STM32-F4VE-V2.0.html STM32-base project page] | * [https://stm32-base.org/boards/STM32F407VET6-STM32-F4VE-V2.0.html STM32-base project page] | ||

* [https://developer.arm.com/open-source/gnu-toolchain/gnu-rm GNU ARM Embedded Toolchain] | * [https://developer.arm.com/open-source/gnu-toolchain/gnu-rm GNU ARM Embedded Toolchain] | ||

* [https://github.com/texane/stlink stlink — ST-Link software] | * [https://github.com/texane/stlink stlink — Open source ST-Link software] | ||

[[Category:Electrónica]] | [[Category:Electrónica]] | ||

Revisão das 22h49min de 12 de março de 2026

Overview

The STM32 F4VE is a small development board based on the STM32F407VET6 microcontroller. It breaks out all CPU pins via two 2×24 pin headers and supports expansion through multiple peripheral connectors.

Board marked "STM32F4XX STM32_F4VE V2.0 1509" on the back.

| Board | |

|---|---|

| Name | STM32 F4VE |

| Part | STM32_F4VE |

| Origin | China |

| PCB Color | Black |

| PCB Size | 62mm × 85mm |

| Mounting | 4× M3 holes |

Warnings

- Warning: The +5V pins are directly connected to the USB +5V pin with no protection. Do not power the board through USB and an external power supply at the same time.

- Warning: The board has an extra pull-up resistor on D+ (R21, 1.5kΩ) that violates the USB specification when the MCU's internal pull-ups are also active. This may cause USB errors. USB data lines also have 22Ω series resistors (R18, R19) for protection.

Microcontroller

| STM32F407VET6 | |

|---|---|

| Manufacturer | ST Microelectronics |

| Core | ARM Cortex-M4 32-bit + FPU |

| Max. Clock | 168 MHz |

| Operating Voltage | 1.8V – 3.6V |

| Package | LQFP100 |

| Memory | |

|---|---|

| Flash | 512 KiB |

| SRAM | 192 KiB |

| Backup SRAM | 4 KiB |

| Oscillators | |

|---|---|

| HSI | 16 MHz |

| LSI | 32 kHz |

| HSE | 8 MHz (Y2) |

| LSE | 32.768 kHz (Y1) |

Peripherals

- 3× SPI

- 3× USART + 2× UART

- 2× I2S

- 3× I2C

- 1× FSMC

- 1× SDIO

- 2× CAN

- 1× USB 2.0 FS/HS (with DMA)

- 1× USB HS ULPI (for external PHY)

- 1× 10/100 Ethernet MAC

- 1× 8–12-bit parallel camera interface

- 3× ADC 12-bit (1 µs)

- 2× DAC 12-bit

- Single-cycle DSP instructions

Board Hardware

Power

| Voltage Regulator — AMS1117-3.3V (U1) | |

|---|---|

| Input | +4.6V to +15V |

| Output | +3.3V @ 1A |

| Package | SOT223 |

| Power Sources | +5V pin, +3.3V pin, USB |

LEDs

| Ref | GPIO | Resistor | Mode |

|---|---|---|---|

| D1 (Power) | +3.3V rail | R5 (510Ω) | Always on |

| D2 (User) | PA6 | R13 (510Ω) | Sink (active low) |

| D3 (User) | PA7 | R14 (510Ω) | Sink (active low) |

Buttons

| Label | GPIO | Mode |

|---|---|---|

| RST | NRST | Active low |

| K_UP | PA0 | Active high |

| K0 | PE4 | Active low |

| K1 | PE3 | Active low |

Boot Mode Jumpers

| Label | Connected to | Notes |

|---|---|---|

| BT0 | BOOT0 | Part of Header 2 (J3, pin 5). GND via R7 by default. |

| BT1 | PB2 (BOOT1) | Part of Header 2 (J3, pin 6). GND via R8 by default. |

Note: Both BOOT pins are pulled to GND by default (R7, R8 = 10kΩ), booting from flash. Jumper caps are pre-installed for convenience.

On-board Devices

| SPI Flash — W25Q16 (U3) | |

|---|---|

| Capacity | 2 MiB (16 Mbit) |

| Interface | SPI1 |

| Package | SOP-8 |

| /CS (F_CS) | PB0 (10kΩ pull-up via R20) |

| DO (MISO) | PB4 / SPI1_MISO |

| DI (MOSI) | PB5 / SPI1_MOSI |

| CLK | PB3 / SPI1_SCK |

| /WP | +3.3V (always writable) |

| /HOLD | +3.3V |

| RTC Backup Battery | |

|---|---|

| Type | CR1220 |

| Protection | BAT54C dual Schottky diode (Q1) |

Connectors & Pinouts

GPIO Headers

Two 2×24 pin headers (2.54mm, male) break out all GPIO.

Note: PB3, PB5, PB6, PB7 are shared with the nRF24L01 header (SPI1). PB3/PB4 are also used for JTAG (TDO/TRST). PA13/PA14 are JTAG only and do not appear on the GPIO headers.

| Pin | GPIO | GPIO | Pin | |

|---|---|---|---|---|

| 1 | 5V | 5V | 2 | |

| 3 | 5V | 5V | 4 | |

| 5 | 3V3 | 3V3 | 6 | |

| 7 | 3V3 | 3V3 | 8 | |

| 9 | GND | GND | 10 | |

| 11 | PE2 | PE3 | 12 | |

| 13 | PE4 | PE5 | 14 | |

| 15 | PE6 | PC13 | 16 | |

| 17 | PC0 | PC1 | 18 | |

| 19 | PC2 | PC3 | 20 | |

| 21 | VREF- | VREF+ | 22 | |

| 23 | PA0 | PA1 | 24 | |

| 25 | PA2 | PA3 | 26 | |

| 27 | PA4 | PA5 | 28 | |

| 29 | PA6 | PA7 | 30 | |

| 31 | PC4 | PC5 | 32 | |

| 33 | PB0 | PB1 | 34 | |

| 35 | PE7 | PE8 | 36 | |

| 37 | PE9 | PE10 | 38 | |

| 39 | PE11 | PE12 | 40 | |

| 41 | PE13 | PE14 | 42 | |

| 43 | PE15 | PB10 | 44 | |

| 45 | PB11 | PB12 | 46 | |

| 47 | PB13 | PB14 | 48 |

| Pin | GPIO | GPIO | Pin | |

|---|---|---|---|---|

| 1 | 3V3 | 3V3 | 2 | |

| 3 | 3V3 | 3V3 | 4 | |

| 5 | BT0 (BOOT0) | BT1 (PB2) | 6 | |

| 7 | GND | GND | 8 | |

| 9 | GND | GND | 10 | |

| 11 | PE1 | PE0 | 12 | |

| 13 | PB9 | PB8 | 14 | |

| 15 | PB7 ¹ | PB6 ¹ | 16 | |

| 17 | PB5 ¹ | PB3 ¹ | 18 | |

| 19 | PD7 | PD6 | 20 | |

| 21 | PD5 | PD4 | 22 | |

| 23 | PD3 | PD2 | 24 | |

| 25 | PD1 | PD0 | 26 | |

| 27 | PC12 | PC11 | 28 | |

| 29 | PC10 | PA15 | 30 | |

| 31 | PA12 | PA11 | 32 | |

| 33 | PA10 | PA9 | 34 | |

| 35 | PA8 | PC9 | 36 | |

| 37 | PC8 | PC7 | 38 | |

| 39 | PC6 | PD15 | 40 | |

| 41 | PD14 | PD13 | 42 | |

| 43 | PD12 | PD11 | 44 | |

| 45 | PD10 | PD9 | 46 | |

| 47 | PD8 | PB15 | 48 |

¹ Shared with nRF24L01 header (SPI1): PB3=SCK, PB5=MOSI, PB6=CE, PB7=CS.

JTAG / SWD Header (P1) — 2×10

| Pin | Function | Function | Pin | |

|---|---|---|---|---|

| 1 | +3.3V | +3.3V | 2 | |

| 3 | TRST (PB4) | GND | 4 | |

| 5 | TDI (PA15) | GND | 6 | |

| 7 | TMS/SWDIO (PA13) | GND | 8 | |

| 9 | TCLK/SWCLK (PA14) | GND | 10 | |

| 11 | RTCK (N.C.) | GND | 12 | |

| 13 | TDO/SWO (PB3) | GND | 14 | |

| 15 | RESET (NRST) | GND | 16 | |

| 17 | N.C. | GND | 18 | |

| 19 | N.C. | GND | 20 |

TFT LCD Header (J1) — 2×16

| Pin | Function | Function | Pin | |

|---|---|---|---|---|

| 1 | GND | RST | 2 | |

| 3 | FSMC_D15 (PD10) | FSMC_D14 (PD9) | 4 | |

| 5 | FSMC_D13 (PD8) | FSMC_D12 (PE15) | 6 | |

| 7 | FSMC_D11 (PE14) | FSMC_D10 (PE13) | 8 | |

| 9 | FSMC_D9 (PE12) | FSMC_D8 (PE11) | 10 | |

| 11 | FSMC_D7 (PE10) | FSMC_D6 (PE9) | 12 | |

| 13 | FSMC_D5 (PE8) | FSMC_D4 (PE7) | 14 | |

| 15 | FSMC_D3 (PD1) | FSMC_D2 (PD0) | 16 | |

| 17 | FSMC_D1 (PD15) | FSMC_D0 (PD14) | 18 | |

| 19 | FSMC_NOE (PD4) | FSMC_NWE (PD5) | 20 | |

| 21 | FSMC_A18 (PD13) | FSMC_NE1 (PD7) | 22 | |

| 23 | Touch_CLK (PB13) | Touch_CS (PB12) | 24 | |

| 25 | Touch_MOSI (PB15) | Touch_MISO (PB14) | 26 | |

| 27 | Touch_PEN (PC5) | LCD_BL (PB1) ² | 28 | |

| 29 | VBAT (N.C.) | GND | 30 | |

| 31 | +3.3V | GND | 32 |

² LCD backlight (PB1) is driven via PNP transistor Q2, not directly.

nRF24L01 Header (JP2) — 2×4

| Pin | Function | Function | Pin | |

|---|---|---|---|---|

| 1 | GND | VCC (+3.3V) | 2 | |

| 3 | CE (PB6) | CSN (PB7) | 4 | |

| 5 | SCK (PB3) | MOSI (PB5) | 6 | |

| 7 | MISO (PB4) | IRQ (PB8) | 8 |

Serial Header (J6) — 1×4

| Pin | Function | GPIO |

|---|---|---|

| 1 | VCC | +5V |

| 2 | GND | Ground |

| 3 | RX | PA10 (USART1_RX) |

| 4 | TX | PA9 (USART1_TX) |

MiniSD Connector (U5)

| Pin | Function | GPIO |

|---|---|---|

| 1 | DAT2 | PC10 (SDIO_D2) |

| 2 | CD/DAT3 | PC11 (SDIO_D3) |

| 3 | CMD | PD2 (SDIO_CMD) |

| 4 | VDD | +3.3V |

| 5 | CLK | PC12 (SDIO_SCK) |

| 6 | VSS | Ground |

| 7 | DAT0 | PC8 (SDIO_D0) |

| 8 | DAT1 | PC9 (SDIO_D1) |

| 9 | CD | N.C. |

Note: SDIO data lines and CMD have 10kΩ pull-up resistors (R24, R26–R29).

USB Mini Connector (J4)

| Pin | Function | GPIO |

|---|---|---|

| 1 | VCC | +5V |

| 2 | D- | PA11 (USB_DM), 22Ω series (R19) |

| 3 | D+ | PA12 (USB_DP), 22Ω series (R18), 1.5kΩ pull-up (R21) |

| 4 | ID | N.C. |

| 5 | GND | Ground |

Development

Toolchain

Generate the project with STM32CubeMX in Makefile format, then compile with the GNU ARM Embedded Toolchain.

Flashing

Use an ST-Link V2 programmer and the stlink software:

st-flash write build/blinky.bin 0x8000000

Debugging

Run st-util in a separate terminal, then launch GDB:

arm-none-eabi-gdb --eval-command="tar extended-remote :4242" build/blinky.elf

Documentation

- Board schematic (ZET6 variant — mostly applicable): Media:STM32F407ZET6_sch-1.pdf

- Note: MCU pin numbers differ; I/O connectors have fewer pins; SDRAM not present on this board.

- Alternative schematic with PCB layout and BOM: Media:STM32_F4VE_SCHEMATIC.PDF

- Original schematic: STM32_F4VE_V2.0 Schematic (stm32-base.org)

- Demo software translated manual: Media:STM32F407_example_manual.ja.en.pdf